采用PLL技術(shù)的接收機射頻前端的設(shè)計

接著對整機進行測試,結(jié)果如下:

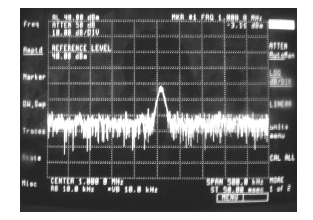

圖7、實際解調(diào)輸出信號

解調(diào)輸出后得到信號頻率為1MHz 的基帶信號。固定AGC 增益值的情況下,即此時衰減值固定為0dBm,改變輸入射頻信號的功率,每增加10dBm,輸出I/Q 信號功率增加約為10dBm,整機線性度[10]良好,注意此時應(yīng)該在較低功率范圍內(nèi)調(diào)節(jié)輸入功率,保證輸出I/Q信號功率不會過大。經(jīng)測試,接收機的最小可接收檢測信號功率約-118dBm。

在接收機中,解調(diào)輸出I/Q 兩路平衡是非常重要的指標。由于接收機信道特性不同,本振信號相位誤差等諸多的因素都會導(dǎo)致I/Q 兩路基帶信號增益不平衡。若I/Q 失配,則會導(dǎo)致I/Q 誤碼率增高,嚴重影響解調(diào)性能。在本設(shè)計中,在選取芯片、設(shè)計電路中充分考慮到此問題,實際I/Q 兩路輸出基本做到了平衡輸出。

5、結(jié)論

本文研究了使用PLL 的接收機原理和實現(xiàn)方案,并成功的用軟硬件平臺對其實現(xiàn)。本文的創(chuàng)新點在于成功的運用兩個鎖相環(huán)電路實現(xiàn)第一、二本振信號,試驗結(jié)果表明鎖相環(huán)有鎖定時間短,相位噪聲小,性能穩(wěn)定等優(yōu)點。實測結(jié)果表明接收機性能良好,指標達到了系統(tǒng)設(shè)計要求。

現(xiàn)代射頻接收機主要是向高線性、大動態(tài)范圍,高靈敏度,高分辨率等方面發(fā)展。如何采取有效的方法來提高接收機的抗干擾能力,降低超外差式接收機的成本,使得整體性能得以改進,是當今研究的熱點方向,對接收機的研究有著非常重要的意義。

作者:牛吉凌,孫利佳

參考文獻

[1] Roy B.《無線通信技術(shù)》[M].北京:科學出版社,2004.

[2] 張玉興.《射頻模擬技術(shù)》[M].北京:電子工業(yè)出版社,2001.

[3] 陳邦媛.《射頻通信電路》[M].北京:科學出版社,2002.

[4] 張猛,章策珉,馬金軍,樓東武.射頻接收機整體噪聲與增益可預(yù)測性設(shè)計[J].無線電工程, 2000,1(2): 13-17.

[5] 張厥盛,鄭繼禹.《鎖相技術(shù)》[M].西安:西安電子科技大學出版社,1996.

[6] Behzard R,

[7] Integrated synthesizer and VCO ADF4360-8, Analog Devices C04414-0-12/04(B), 2004.

[8] Derek K S, The design and implementation of low-power CMOS radio receivers [J]. PhD Thesis, 1998, 17(2):41-46.

[9] Reinhold L P,

[10] Gonzalez G, Micro transistor amplifiers: analysis and design [J]. Englewood Cliffs, NJ: Pretice-Hall, 1984:91-44.

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號